# DAP 1200a & DAP 2400a Manual

Installation Guide and Connector Reference

Version 1.00

Microstar Laboratories, Inc.

This manual contains proprietary information which is protected by copyright. All rights are reserved. No part of this manual may be photocopied, reproduced, or translated to another language without prior written consent of Microstar Laboratories, Inc.

Copyright © 1985 - 2000

Microstar Laboratories, Inc. 2265 116 Avenue N.E. Bellevue, WA 98004 Tel: (425) 453-2345 Fax: (425) 453-3199 http:// www.mstarlabs.com

Microstar Laboratories, DAPcell, Data Acquisition Processor, DAP, DAPL, and DAPview are trademarks of Microstar Laboratories, Inc.

Microstar Laboratories requires express written approval from its President if any Microstar Laboratories products are to be used in or with systems, devices, or applications in which failure can be expected to endanger human life.

Microsoft, MS, and MS-DOS are registered trademarks of Microsoft Corporation. Windows is a trademark of Microsoft Corporation. IBM is a registered trademark of International Business Machines Corporation. Intel is a registered trademark of Intel Corporation. Novell and NetWare are registered trademarks of Novell, Inc. Other brand and product names are trademarks or registered trademarks of their respective holders.

Part Number MSHM002-01

# Contents

| Contents                                        | iii |

|-------------------------------------------------|-----|

| 1. Introduction                                 | 1   |

| About This Manual                               |     |

| 2. Installation, Testing, & Troubleshooting     |     |

| Data Acquisition Processor Handling Precautions |     |

| System Requirements                             |     |

| Standard Configurations                         |     |

| Installing the Data Acquisition Processor       |     |

| To Install the Data Acquisition Processor:      |     |

| Installing DAP Software                         |     |

| To Install Data Acquisition Processor Software: | 5   |

| Testing Installation                            | 6   |

| Troubleshooting                                 | 7   |

| 3. Advanced Installation Options                | 11  |

| Nonstandard Configurations                      | 11  |

| The INSTALL Program                             | 13  |

| Device Driver Configuration                     | 15  |

| The ACOMINIT Program                            |     |

| Com Pipe Configuration                          | 16  |

| P Parameter Size                                |     |

| DAP-to-DAP Communication                        |     |

| The DAPLINIT Program                            |     |

| Installing Several Data Acquisition Processors  |     |

| Installation on a Network                       |     |

| DAPL Licensing                                  |     |

| Removing Data Acquisition Processor Software    |     |

| 4. DAP 1200a & DAP 2400a Connectors             |     |

| Analog Input/Output Connector                   |     |

| Digital Input/Output Connector                  |     |

| Output Clock Connector                          |     |

| Shunts                                          |     |

| Analog Signal Path Selection                    |     |

| Analog Signal Path Configuration                |     |

| Channel List Selection                          |     |

| Analog Output Voltage Range Selection           |     |

| Digital Output Reset Polarity Jumper            |     |

| Input/Output Synchronization Header             |     |

| Synchronization Connector                       |     |

| 5. Analog Input Circuits                        |     |

| Analog Input Circuits                           |     |

| Programmable Gain Amplifier                     | 44  |

Contents

| 6. Clocks and Triggers                                 | 45 |

|--------------------------------------------------------|----|

| Software Triggers vs. Hardware Triggers for Input      | 45 |

| External Input Clock                                   | 46 |

| Early External Input Clock Edges                       | 48 |

| Input Pipeline Timing                                  | 49 |

| External Output Clock                                  | 50 |

| Hardware Input Trigger                                 | 50 |

| Hardware Output Trigger                                | 52 |

| Timing Considerations                                  | 53 |

| Input Clocking Startup Considerations                  | 53 |

| Using the Input Trigger with External Input Clocking   | 54 |

| Using the Output Trigger with External Output Clocking | 54 |

| Timing tables                                          |    |

| 7. Recalibration                                       | 57 |

| CALDAP                                                 | 57 |

| Equipment Requirements                                 | 58 |

| Connector Numbering                                    |    |

| Preparing the Data Acquisition Processor               | 59 |

| Starting CALDAP                                        | 59 |

| Calibrating the Data Acquisition Processor             |    |

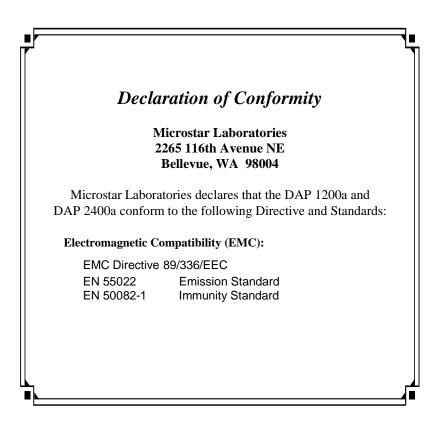

| Appendix A: Declaration of Conformity                  | 63 |

| Index                                                  | 65 |

Contents

# **1. Introduction**

The Data Acquisition Processor from Microstar Laboratories is a complete data acquisition system that occupies one expansion slot in a PC. Data Acquisition Processors are suitable for a wide range of applications in laboratory and industrial data acquisition and control.

Both the DAP 1200a and DAP 2400a:

- have an onboard Intel 80C188XL processor

- sample data at up to 312K samples per second.

- update analog or digital outputs at up to 312K samples per second.

- transfer data to the PC at up to 312K samples per second.

- are compatible with other a-Series Data Acquisition Processors.

In addition, the DAP 2400a has a Motorola DSP 56001 coprocessor.

The DAP 1200a and DAP 2400a use DAPL as the onboard operating system, which is optimized for the 16-bit processors used by these boards.

# **About This Manual**

This manual includes hardware and software installation instructions and a hardware connector reference. Three other manuals provide information about creating data acquisition applications:

- The DAPL Manual contains a complete DAPL reference.

- The Applications Manual contains many useful examples of Data Acquisition Processor applications.

- The Systems Manual describes support software that runs in the PC, including support for writing programs that run in the PC.

Introduction

# 2. Installation, Testing, & Troubleshooting

Installing a Data Acquisition Processor involves the following steps:

- 1. If necessary, change jumper settings on the Data Acquisition Processor.

- 2. Install the Data Acquisition Processor.

- 3. Install the DAP Software.

- 4. Test the Installation.

Installation instructions are provided in this chapter. Advanced installation information is provided in Chapter 3. If there are any problems with installation, please read the troubleshooting guide at the end of this chapter.

# **Data Acquisition Processor Handling Precautions**

Static control is required for handling all electronic equipment. The Data Acquisition Processor is especially sensitive to static discharge because it contains many highspeed analog and digital components. To protect the Data Acquisition Processor, observe the following precautions:

- Wear a grounding strap when handling the Data Acquisition Processor. If it is not possible to use a grounding strap, continuously touching a metal screw on a grounded PC offers protection.

- If it is necessary to transport the Data Acquisition Processor outside of the PC, be sure to shield the Data Acquisition Processor in a conductive plastic bag. If a conductive bag is not available, shield the Data Acquisition Processor by wrapping it completely in aluminum foil. Do not ship or store a Data Acquisition Processor in plastic peanuts without suitable shielding.

Static damage to analog components can cause subtle problems, including oscillation, increased settling time, and reduced slew rate. If you suspect that a Data Acquisition Processor has been affected by static discharge, return it to Microstar Laboratories for testing, repair, and quality control.

# **System Requirements**

The Data Acquisition Processor is compatible with 16-bit ISA or 32-bit EISA slots in AT/386/486/Pentium computers and requires version 3.0 or higher of DOS.

# **Standard Configurations**

The Data Acquisition Processor is factory-configured to use interrupt 2 and I/O addresses in the range 220-22F (hexadecimal). This configuration does not conflict with most standard PC hardware. If you have nonstandard PC hardware or if any installed cards that use the same interrupt vector or I/O address as the Data Acquisition Processor, please read Chapter 3 before preceding with installation.

Note: Some sound cards are known to use I/O addresses in the 220-22F range. If your system has a sound card, check the configurations.

Interrupt and I/O address conflicts may cause subtle or obvious problems in your PC. After installing the Data Acquisition Processor, if your PC does not operate properly, check that there are no configuration conflicts.

# **Installing the Data Acquisition Processor**

Caution: Do not install the Data Acquisition Processor while the PC is on.

#### To Install the Data Acquisition Processor:

1. Make any necessary changes to the hardware settings. Interrupt vector and I/O address information is provided in Chapter 3. Chapter 4 provides information about setting other hardware options. The default hardware settings are correct for msot systems.

2. Turn off the PC and remove the PC's cover.

3. Insert the Data Acquisition Processor into any free slot.

The Data Acquisition Processor requires approximately 15 Watts from the PC's power supply. If your system behaves erratically with the Data Acquisition Processor installed, the PC may need a larger power supply.

# **Installing DAP Software**

Before installing the DAP Software, make backup copies of the diskette(s). Put the originals in a safe place, and use the backup disks for installation.

#### To Install Data Acquisition Processor Software:

- 1. Install the Data Acquisition Processor, as previously described.

- 2. Insert the DAP software disk into the PC's diskette drive.

- 3. At the DOS prompt, type A: /I NSTALL.

- 4. Follow the on-screen instructions.

INSTALL prompts for configuration information including Data Acquisition Processor type and software destination directories. INSTALL provides information about each step to guide you through the installation process and provides options for copying DAPview and other software and Data Acquisition Processor support software to your PC.

INSTALL copies several files to your boot disk and adds information to your system configuration files CONFIG. SYS and AUTOEXEC. BAT. Backup copies of these files are created with the . BAK extension so that the original versions can be recovered.

# **Testing Installation**

After running the INSTALL program, verify that software installation was successful by rebooting your PC. Before you see the DOS prompt, the following lines should appear on your screen:

ACCEL device driver 4.3 ACCEL driver initialization completed DAPL initialization completed

The exact lines may vary slightly, depending upon configuration options. If a line is missing or if an error message appears, see the Troubleshooting section in this chapter.

When the DOS prompt is displayed, set the current directory to your DAPview directory and run DAPview by entering the following command:

DV

DAPview allows you to communicate interactively with the Data Acquisition Processor. Now everything you type at the PC keyboard is sent to the Data Acquisition Processor and all Data Acquisition Processor messages are printed on your screen. When the DAPview program begins, the following lines should be displayed on your screen:

\*\*\* DAPview [1.2] \*\*\* \*\*\* DAPL Interpreter [4.XX XX/X] Serial# XXXXX \*\*\* #

The appearance of the # prompt indicates that the Data Acquisition Processor is installed correctly. If the # prompt does not appear or if DAPview issues an error message and terminates, you have not established communication with the Data Acquisition Processor. Turn to the end of this chapter for troubleshooting hints.

Note: To exit from DAPview, press the Ctrl and Z keys simultaneously.

The number sign (#) indicates that the Data Acquisition Processor is waiting for a command. At this time you can enter DAPL commands from the keyboard or load DAPL command files. Sample applications are provided in the Applications Manual. The Systems Manual contains more information about DAPview.

# Troubleshooting

The Systems Manual contains a list of the error messages which may be printed during software installation and system boot. The following errors commonly result from installation problems:

INSTALL prints an error message.

Find the error message in the "System Messages" chapter of the Systems Manual.

At system startup, the "ACCEL device driver 4.3" message is not printed.  $\ensuremath{\mathsf{OR}}$

$\mathsf{DAPview}\xspace$  prints the error message "Host communication port is uninitialized"

Check that the file CONFIG. SYS is present on your boot volume. If this file was not present before installation, it should have been placed on your boot volume by INSTALL. If the file CONFIG. SYS is present, check that it includes the line

DEVICE=x: \yyy\ACOM. SYS . . .

The "x" character should be the letter of your boot disk. "yyy" should be the correct directory where the file ACOM. SYS is located. If CONFIG. SYS is not on your boot volume, or if the ACOM. SYS line of the file CONFIG. SYS is incorrect, use INSTALL again, being careful to install the software on the correct volume.

The message "Bad or missing ACOM. SYS" is printed.

The file ACOM. SYS probably was not copied by INSTALL from the Data Acquisition Processor diskette to your boot volume. Use INSTALL again, being careful to install the software on the correct volume.

When your system is booted, one of the following messages is printed:

DAP hardware not found or improperly configured

DAP interrupt conflict

DAP interrupt selection error

These messages suggest a hardware conflict with another card in the PC; one or more of the Data Acquisition Processor configuration jumpers may need to be changed to resolve the conflict. See Chapter 3.

At system startup, the message "ACCEL driver initialization completed" is not printed.

If an error message is printed by the ACOMINIT program, find the error message in the Systems Manual. If no error message is printed, check that the AUTOEXEC. BAT file on your boot volume contains a line beginning with the command ACOMINIT. If no ACOMINIT line is found, use INSTALL again, being careful to install the software on the correct volume.

At system startup, the message "DAPL initialization completed" is not printed.

If an error message is printed by the DAPLINIT program, find the error message in the Systems Manual. If no error message is printed, check that the AUTOEXEC. BAT file on your boot volume contains a line beginning with the command DAPLINIT. If no DAPLINIT line is found, use the INSTALL pro-gram again, being careful to install the software on the correct volume.

DAPview issues the error message "Could not establish communications" OR DAPview does not display a DAPL # prompt.

The Data Acquisition Processor is not communicating with your PC. This may indicate that an error occurred at boot time. Check that no error messages are printed when you boot your system.

If your PC has cards other than those listed at the beginning of the chapter, a card may be interfering with communications. Remove optional cards, boot the PC, and try using DAPview again.

Check that the configuration jumpers on the Data Acquisition Processor are correct. See Chapter 3 for the correct jumper selections. Check also for consistency between the jumper settings and the settings on the ACOM. SYS line in the file CONFIG. SYS.

A final possibility is that the Data Acquisition Processor may be faulty. If you suspect that this is the case, call Microstar Laboratories. When calling for installation support, please open your PC case so that the Data Acquisition Processor jumpers are visible, and be ready to provide the following information:

- the serial and model numbers of your Data Acquisition Processor.

- the contents of your AUTOEXEC.BAT and CONFIG.SYS files.

- a list of all hardware boards installed in your computer.

Your PC keyboard locks up when DAPview is started and does not accept the Ctrl-Z key.

Your PC may have an old style keyboard. Try starting DAPview with one of the following command line options:

DV /K1 DV /K2

DAPvi ew i ssues the error "Help file DV. HLP not found." Check that the file DV. HLP has been copied to the directory containing the DAPview files. Check also to make sure the file AUTOEXEC. BAT has the line:

SET DV=C: \DV

Replace C: \DV with the drive and directory containing the DV. HLP file.

# **3. Advanced Installation Options**

Installation for standard hardware configurations is described in Chapter 2. This chapter covers installation in more detail.

# **Nonstandard Configurations**

The Data Acquisition Processor uses two resources from the host PC:

- an interrupt vector

- a range of I/O addresses

The Data Acquisition Processor allows several interrupt vector and I/O address selections. The interrupt vector may be 2, 3, 4, or 5. When selecting an interrupt vector, note the following interrupt vectors used by standard cards:

| EGA/VGA                        | 2 |

|--------------------------------|---|

| serial port COM2               | 3 |

| serial port COM1               | 4 |

| parallel port #2               | 5 |

| hard disk controller on IBM XT | 5 |

| parallel port #1               | 7 |

The Data Acquisition Processor is shipped configured to use interrupt 2. EGA and VGA video adapters potentially can use interrupt 2, but most applications do not use this capability. Since interrupt 2 does not conflict with any other standard hardware, this is the default Data Acquisition Processor interrupt vector.

If any other cards are installed, determine the interrupts used and select a Data Acquisition Processor interrupt number distinct from these. Depending on the selection, the host computer may lose access to one of the serial COM ports or one of the parallel ports.

To change interrupt vectors, locate the 16-pin HOST CONFI GURE connector:

| 1<br>●        | 2<br>•        | 3             | 4<br>•        | 5<br>9        | 6<br>\$       | 7<br>©        | 8             |  |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--|

| <b>e</b><br>1 | <b>9</b><br>2 | <b>e</b><br>3 | <b>9</b><br>4 | <b>9</b><br>5 | <b>e</b><br>6 | <b>9</b><br>7 | <b>e</b><br>8 |  |

| J10           | Н             | IOS           | тс            | ON            | IFIC          | GUF           | RE            |  |

This connector is directly above the gold fingers on the Data Acquisition Processor printed circuit board.

#### **Advanced Installation Options**

11

The following table gives the four possible interrupt selections:

| Interrupt Vector | Jumper     |

|------------------|------------|

| 2                | pin pair 7 |

| 3                | pin pair 4 |

| 4                | pin pair 5 |

| 5                | pin pair 6 |

To change the interrupt, remove the jumper and replace it according to this table. Note that exactly one of the pin pairs 4, 5, 6, and 7 should be connected.

When the interrupt is changed, the INSTALL program must be informed of the new interrupt selection. When running INSTALL, select the DAP 0 button and select the interrupt number that matches the interrupt of the Data Acquisition Processor.

In addition to an interrupt vector, the Data Acquisition Processor uses a range of I/O addresses. If a sound card or any nonstandard cards are used in the host PC, check that the Data Acquisition Processor I/O addresses do not conflict with those cards.

The Data Acquisition Processor is shipped configured to use I/O addresses in the range 220-22F (hexadecimal). This range may be changed by changing the jumpers on the HOST CONFI GURE connector. Pin pairs 1, 2, and 3 select the I/O address of the Data Acquisition Processor according to the following table:

| Jumpers |

|---------|

| 1, 2, 3 |

| 2, 3    |

| 1, 3    |

| 3       |

| 1, 2    |

| 2       |

| 1       |

|         |

When the I/O address is changed, the INSTALL program must be informed of the new address selection. When running INSTALL, select the DAP 0 button and select the address that matches the address of the Data Acquisition Processor.

Note: The only effect of changing the interrupt number or address in the INSTALL program is to change the value of the /1 or /A parameter of the line ACOM. SYS that is inserted in the file CONFIG. SYS.

### The INSTALL Program

This section provides additional details about the INSTALL program. This information is of interest only to advanced Data Acquisition Processor users.

The INSTALL program installs Data Acquisition Processor software on a PC and configures the PC to initialize the ACCEL driver when the PC boots. INSTALL uses the following syntax:

A: INSTALL <options>

If installing from a drive other than A: , type the letter for that drive instead. INSTALL allows several command line options for special installation features. The following options are legal:

| /COMx | Use serial port communication on com port x (DAP 801 only) |

|-------|------------------------------------------------------------|

| /Mxx  | Default ACCEL driver mode (See the Systems Manual)         |

| /Dx   | Install more than one DAP                                  |

| /?    | Help                                                       |

When running INSTALL, several prompts are provided for configuring Data Acquisition Processor software on a PC. Select a DAP button to choose the DAP model, address, and interrupt for the Data Acquisition Processor. Choose the Select Software Options button to select the specific software options to install. For help on the options press F1.

After all options have been verified, INSTALL copies Data Acquisition Processor software to the PC and modifies the system files. INSTALL copies the files ACOM. SYS, ACOMINIT. EXE, DAPLINIT, and Dx-x. STD to the PC boot drive. INSTALL creates the file ACOM. DAT and places it on the boot drive. These files are all placed on the boot drive so they are available when the PC first boots.

After copying the boot files, INSTALL copies the software that was specified in the Select Software Options dialog box to the Main directory.

INSTALL adds a line to the file CONFIG. SYS that loads the ACCEL device driver. If this line already exists from a previous installation, INSTALL replaces it. The following line is a typical line that INSTALL adds to CONFIG. SYS:

device=c: \dap\acom. sys i2 dap: a220 m20 p1A4

More information about the ACCEL driver configuration line is provided later in this chapter. If CONFIG. SYS does not exist, INSTALL creates it. Before modifying CONFIG. SYS, INSTALL saves an original copy in the file CONFIG. BAK.

Advanced Installation Options

13

INSTALL also modifies the file AUTOEXEC. BAT by adding several lines that configure the ACCEL driver with specific communication information. If these lines already exist from a previous installation, INSTALL replaces them. The following lines are typical lines that INSTALL adds to AUTOEXEC. BAT:

c:\dap\acominit c:\dap\acom.dat @if errorlevel 1 pause c:\dap\daplinit /reset c:\dap\d\*.std @if errorlevel 1 pause

The ACOMINIT program configures the ACCEL driver with specific communication pipe information provided by the file ACOM. DAT. For some Data Acquisition Processor models, the DAPLINIT program is required to initialize the DAPL operating system. More information about the ACOMINIT and DAPLINIT programs is provided later in this chapter. If AUTOEXEC. BAT does not exist, INSTALL creates it. Before modifying AUTOEXEC. BAT, INSTALL saves an original copy in the file AUTOEXEC. BAK.

# **Device Driver Configuration**

This section explains the format of the device driver command that is placed in the CONFIG. SYS file by the INSTALL program. This information is of interest only to advanced programmers.

The format of the device driver command is:

```

DEVICE=ACOM. SYS [Ix] [DAP[yyy]: Azzz] [Muu] [Pwww]

```

Note: Several parameters are optional. The letters u through z in each parameter represent hexadecimal digits.

x specifies the interrupt vector that is used for PC communication. This number should match the configuration of jumper J10 on the Data Acquisition Processor.

The ACCEL driver automatically detects the type of Data Acquisition Processor that is installed. yyy is optional and manually specifies the board type. For the DAP 1200a, yyy is 1200a. For the DAP 2400a, yyy is 2400a.

zzz specifies the hexadecimal starting I/O address of the Data Acquisition Processor. This number must match the configuration of jumper J10 on the Data Acquisition Processor.

uu is a hexadecimal number that specifies the default mode of the ACCEL driver. See the Systems Manual for more information about ACCEL driver modes.

www is a hexadecimal number that specifies the number of paragraphs of memory to reserve for PC communications pipes. See "Com Pipe Configuration" later in this chapter.

The following is a typical ACCEL driver command line:

device=c: \dap\acom. sys i2 dap: a220 m20 p1A4

The ACCEL driver can be loaded into high memory with the DOS devi cehi gh statement. See your DOS manual for details on loading device drivers into high memory.

### The ACOMINIT Program

ACOMINIT configures the ACCEL driver communication pipes. ACOMINIT is placed in the file AUTOEXEC. BAT to configure the ACCEL driver when the PC first boots. The syntax for ACOMINIT is:

ACOMINIT <cfg\_file>

<cfg\_file> provides communication pipe configuration information. <cfg\_file> normally is named ACOM. DAT. The following section describes the contents of ACOM. DAT.

### **Com Pipe Configuration**

This section describes the format of communication pipe configuration in the file ACOM. DAT. This information is not required for most applications. During initialization, the Microstar Laboratories program ACOMINIT reads the contents of a configuration file which specifies a com pipe configuration. The configuration file determines the connection between com pipes on the Data Acquisition Processor and com pipes on the PC. Lines in the configuration file have the following syntax:

```

<source> -> <destination> [<options>]

```

<source> and <destination> are specifications of communication pipe locations. A com pipe location is either a Data Acquisition Processor com pipe, a PC com pipe, or a PC serial port:

(DAP[n] CPIPE v) (PC CPIPE w)

n is the Data Acquisition Processor number when several boards are installed in one PC. v is a DAPL com pipe number, w is a PC com pipe number. The space before v and w can be omitted.

For example, the following lines connect the default text input and text output com pipes of the Data Acquisition Processor to the PC:

(dap cpipe 0) -> (pc cpipe 0) (pc cpipe 0) -> (dap cpipe 0)

The first line connects DAPL output com pipe 0 to PC input com pipe 0. The second line connects PC output com pipe 0 to DAPL input com pipe 0. By default, DAPL

**Advanced Installation Options**

16

defines two input com pipes and two output com pipes. Output com pipe 0, named \$SYSOUT, is for text output to the PC. Output com pipe 1, named \$BI NOUT, is for binary output to the PC. Input com pipe 0, named \$SYSI N, is for text input from the PC. Input com pipe 1, named \$BI NI N, is for binary input from the PC.

Each line in the com pipe configuration file may contain one or more options, enclosed in square brackets. The following options are available:

BINARY|TEXT MAXSIZE=xx WIDTH BYTE | WORD | LONG

BI NARY and TEXT specify the type of the data in the com pipe. The default is TEXT.

MAXSI ZE specifies the size of the PC buffer of the com pipe, in bytes. The default is 1024 bytes. The INSTALL program sets the maximum size of the com pipes to be relatively small to conserve PC memory yet provide good performance. The Data Acquisition Processor automatically provides additional pipe buffering when needed. In some applications, increasing the maximum com pipe size can improve performance by allowing larger block operations. Performance can increase with com pipe sizes up to 4096 or 8192. Larger com pipe sizes typically do not provide further performance benefits.

WI DTH specifies the width of data items that are transferred through the com pipe. The WI DTH option must match the width of the corresponding Data Acquisition Processor com pipe. BYTE is the default for text com pipes and also is the only width allowed. WORD is the default for binary com pipes. Any width is allowed for binary com pipes.

The default com pipe configuration file generated by the INSTALL program is stored in the file ACOM. DAT. If the Data Acquisition Processor is operated inside a PC, the following configuration is placed in the file ACOM. DAT:

(dap0 cpi pe0) -> (pc cpi pe0) [text maxsi ze=1024] (pc cpi pe0) -> (dap0 cpi pe0) [text maxsi ze=1024] (dap0 cpi pe1) -> (pc cpi pe1) [bi nary maxsi ze=2048] (pc cpi pe1) -> (dap0 cpi pe1) [bi nary maxsi ze=1024]

In some applications, additional com pipes need to be defined. More com pipes are needed when extra com pipes are defined in DAPL on a Data Acquisition Processor or when several Data Acquisition Processors are installed.

For special applications, extra com pipes can be defined in DAPL. See the CPI PE command in the DAPL Manual.

Note that in many cases, the commands MERGE, MERGEF, and NMERGE can be used instead of defining extra com pipes. It is best to use standard com pipes when possible to maintain a standard communication setup.

When more than one Data Acquisition Processor is installed in a system, additional com pipes need to be defined. For several Data Acquisition Processors, the following com pipe numbering is recommended:

DAPO system text pipe is PC com pipe #0 system binary pipe is PC com pipe #1 DAP1 system text pipe is PC com pipe #2 system binary pipe is PC com pipe #3

DAP6

system text pipe is PC com pipe #12

system binary pipe is PC com pipe #13

### **P** Parameter Size

In a system with additional com pipes, the memory available to the ACCEL driver must be increased. The P parameter in the ACOM. SYS line of the file CONFIG. SYS specifies the number of paragraphs of PC memory reserved for the ACCEL driver and com pipes. The storage requirement of the ACCEL driver and PC com pipes, in bytes, is:

storage = 830 + (maxsize in bytes) + (number of com pipes)\*190

MaxSi ze in bytes is the sum of all com pipe sizes defined in the file ACOM. DAT. Number of com pipes is the number of com pipes defined.

Note: This storage requirement applies for version 4.34 of the ACCEL driver. Subsequent driver versions may require additional storage.

The P parameter is a hexadecimal number, specified in paragraphs. A paragraph of PC memory is 16 bytes. To determine the P parameter, divide the storage requirements by 16 and convert to hexadecimal.

The following example calculates the P parameter for the default ACOM. DAT file created by INSTALL. The result, in bytes, is divided by 16 to get the P parameter in paragraphs.

storage = 830 + 5120 + 4\*190 = 6710 bytes p= 6710/16 = 420 paragraphs (decimal) = 1A4 (hex)

When defining additional com pipes, remember to define pipes for both the DAP-to-PC and PC-to-DAP direction. Some programs such as DAPview for Windows expect additional com pipes defined for both directions.

# **DAP-to-DAP Communication**

Communication pipes can be configured to allow communication between two Data Acquisition Processors. DAP-to-DAP communication occurs over the PC bus in the background with no PC program intervention required. The following syntax is used in the file ACOM. DAT to configure DAP-to-DAP communication:

(DAPw CPIPEx) -> (DAPy CPIPEz) (DAPy CPIPEz) -> (DAPw CPIPEx)

w is the number of the DAP that sends data. x is the DAP communication pipe used to send data. y is the number of the DAP that receives data. z is the DAP communication pipe to receive data. The DAPL command CPI PE is needed to define the DAP communication pipes on each DAP.

The following example shows how to configure a system for DAP-to-DAP communication. This example configures two DAPs. DAP 0 samples one channel of data and sends the data to DAP 1 for analog output.

In the file ACOM. DAT, add:

| (dap0 | cpi pe15) | -> | (dap1 | cpi pe15) | [bi nary | maxsize=1024] |

|-------|-----------|----|-------|-----------|----------|---------------|

| (dap1 | cpi pe15) | -> | (dap0 | cpi pe15) | [bi nary | maxsize=1024] |

DAP-to-DAP com pipes require twice the storage space as DAP-to-PC or PC-to-DAP com pipes. For the above DAP-to-DAP com pipe definition, the P parameter in CONFIG. SYS must be increased by 130 (hex). The following example calculates the P-parameter increase:

storage increase= 2 \* (2048 + 2 \* 190) = 4856 (decimal) p increase=4856/16 = 304 paragraphs (decimal) = 130 (hex)

The following DAPL commands provide an example of how to implement DAP-to-DAP communication.

; DAPL commands for DAP 0: CPIPE TODAP1 PC NUM=15 OUTPUT BINARY WORD RESET IDEF A 1 SET I PI PEO SO TIME 10000 END PDEF B COPY(IPIPEO, TODAP1) END START A, B ; DAPL commands for DAP 1: CPIPE FROMDAPO PC NUM=15 INPUT BINARY WORD RESET PDEF A COPY(FROMDAPO, \$BINOUT) END START A

# The DAPLINIT Program

DAPLINIT initializes the DAPL operating system on the Data Acquisition Processor by downloading a binary image of DAPL to the Data Acquisition Processor. ACCEL driver communication pipes must be configured using ACOMINIT before DAPLINIT is run. The syntax for DAPLINIT is as follows:

DAPLINIT [/RESET] [<dapl\_file>] [<dapl\_file>]\*

<dapl\_file> specifies a binary file containing DAPL. DAPLINIT allows several DAPL binary files to initialize several Data Acquisition Processors in a PC.

The optional parameter /RESET requests a hardware reset of the Data Acquisition Processor before downloading DAPL. If /RESET is not specified, all Data Acquisition Processors retain their state during a warm PC boot.

DAPLINIT detects the Data Acquisition Processor model types on the ACOM. SYS line of the file CONFIG. SYS. DAPLINIT downloads the DAPL files, in order, to the Data Acquisition Processors that require DAPL initialization.

DAPLINIT can accept a wildcard file specification to allow flexibility for when DAP installations change. With a wildcard file name, DAPLINIT searches the current directory and the DOS PATH to find a DAPL binary file that matches the DAP type that is installed. The following example shows how DAPLINIT can be configured to search for the correct DAPL/STANDARD binary file.

DAPLINIT /RESET D\*. STD

The INSTALL program automatically configures new installations to use a wildcard file name for DAPLINIT.

# **Installing Several Data Acquisition Processors**

Up to seven Data Acquisition Processor boards can operate simultaneously in one PC. Running several boards in parallel increases the maximum sampling rate and the realtime processing power of a system. For special options to install up to 14 Data Acquisition Processor boards in one PC, contact Microstar Laboratories.

Each Data Acquisition Processor requires one PC slot. All the Data Acquisition Processors in a PC share just one interrupt line; no DMA lines are required. The Data Acquisition Processors are distinguished by their I/O addresses in the PC. Before installing Data Acquisition Processors in the PC, select a distinct I/O address for each board.

There are seven possible I/O addresses; this limits the number of Data Acquisition Processors in a PC to seven. Set the I/O addresses with the jumpers on the HOST CONFIGURE connector. Information about the HOST CONFIGURE connector is provided at the beginning of this chapter.

Note: Pin pair 8 of the HOST CONFIGURE connector sets the level of the PC's interrupt line. Pin pair 8 must be connected for one Data Acquisition Proc-essor in a PC, and must not be connected for all other Data Acquisition Processors.

INSTALL can perform installation for several Data Acquisition Processors. When typing the INSTALL command, add the option /Dx to the end of the command, where x is the number of boards. For example, the following line defines installation for three Data Acquisition Processors.

A: I NSTALL /D3

INSTALL provides on-screen options for configuring each Data Acquisition Processor individually. Select a DAP button to display a dialog box for choosing the Data Acquisition Processor model, address, and interrupt.

Note: The order in which the boards appear in the ACOM. SYS line in the file CONFIG. SYS determines the numbering of the Data Acquisition Processors. The first Data Acquisition Processor is DAP 0, the second is DAP 1, etc. The addresses do not matter when determining the numbering. When synchronous operation is used with DLOG, the last board in the list is the master unit.

# Installation on a Network

Data Acquisition Processor software can be installed on a network consisting of PC workstations connected to one or more servers. The INSTALL program can copy Data Acquisition Processor software to a PC workstation from a network that has a copy of the DAP Software disk image.

Note: When using Data Acquisition Processor software on a network, each simultaneous user must have a licensed copy of the software.

When installing Data Acquisition Processor software from a network, INSTALL copies several files to the PC workstation boot drive. The files are ACOM. SYS, ACOMINIT. EXE, ACOM. DAT, and, if necessary, DAPLINIT. EXE and Dx-x. STD. These files must be on the PC boot drive so that they are available immediately at boot time. INSTALL copies the remaining Data Acquisition Processor software to a network drive for use once the network is connected. INSTALL modifies AUTOEXEC. BAT and CONFIG. SYS on the workstation boot drive as in regular installations.

# **DAPL Licensing**

When a Data Acquisition Processor is shipped from the factory, a copy of DAPL is provided that is licensed to run on the Data Acquisition Processor. When a DAP Software Upgrade is shipped, the DAPL file on the upgrade is licensed to be used with the Data Acquisition Processor that was specified when the upgrade was ordered.

# **Removing Data Acquisition Processor Software**

When a Data Acquisition Processor is removed from a PC, the software can be removed as well. This section describes how to remove a Data Acquisition Processor software installation.

1. Delete the directory where Data Acquisition Processor software was in-stalled. Usually this directory is c: \dap. Delete all the subdirectories under the DAP directory. Make sure that there are no important data files in these directories before deleting them.

2. Edit the file AUTOEXEC. BAT. Delete the following four lines:

c: \dap\acominit c: \dap\acom. dat @if errorlevel 1 pause c: \dap\daplinit /reset c: \dap\d\*. std @if errorlevel 1 pause

3. Edit the file CONFIG. SYS. Delete the following line:

device=c: \dap\acom. sys i2 dap: a220 m20 p1A4

# 4. DAP 1200a & DAP 2400a Connectors

This chapter discusses the interface connectors on the DAP 1200a and DAP 2400a. Diagrams and documentation for the analog input/output connector, the digital input/output connector, the output clock connector, and jumpers the are provided in this chapter.

Detailed instructions for setting the following options are provided in this chapter:

- the analog input voltage range (J7 & J8)

- the output voltage ranges of DAC0 and DAC1 (J11 and J12)

- the digital output polarity at power-on (J32)

- input/output synchronization (J22)

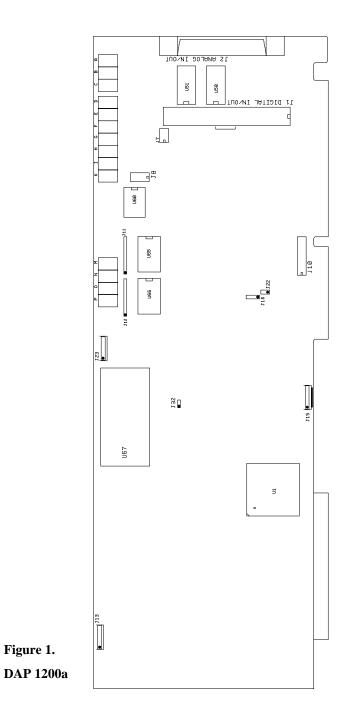

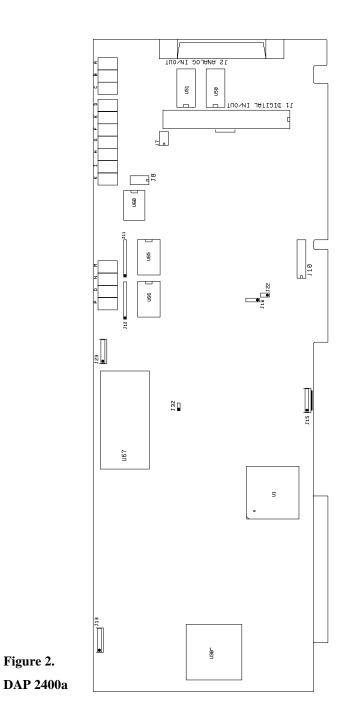

Figure 1 and Figure 2 show component placement outlines of the DAP 1200a and the DAP 2400a. The only components shown are connectors, whose labels begin with the letter J, some integrated circuits, whose labels begin with the letter U, and trim potentiometers, whose labels are single letters.

DAP 1200a & DAP 2400a Connectors

# **Analog Input/Output Connector**

Analog voltages are connected to the Data Acquisition Processor through a 68-pin connector on the back panel of the PC. This connector is located on the right side of the Data Acquisition Processor and is labeled J2 ANALOG I N/OUT. It has a double row of pins on 0.050 inch centers. The connector is 3M part number 10268-52E2VC or AMP part number 2-178238-8. It mates with discrete wire connector 3M part number 10168-6000EC or AMP 2-175677-8. Both connectors are shielded and are compatible with round cable. The analog I/O connector also mates with insulation displacement ribbon cable connector 3M part number 10168-8100EE. The insulation displacement connector is compatible with 0.025" pitch ribbon cable.

Looking at the analog connector from the back of a PC, the pin numbering is:

DAP -18V 35 - - 34 DAP +18V DAC 0 OUT 36 - 33 DAC 0 GROUND DAC 1 OUT 37 - 32 DAC 1 GROUND S15 (D7+) 38 - 31 G15 (G7+) S14 (D7-) 39 = = 30 G14 (G7-) S13 (D6+) 40 = 29 G13 (G6+) S12 (D6-) 41 🗆 🗆 28 G12 (G6-) S11 (D5+) 42 - 27 G11 (G5+) S10 (D5-) 43 = 26 G10 (G5-) S9 (D4+) 44 🗆 🗆 25 G9 (G4+) S8 (D4-) 45 = 24 G8 (G4-) S7 (D3+) 46 = = 23 G7 (G3+) S6 (D3-) 47 = 22 G6 (G3-) S5 (D2+) 48 - 21 G5 (G2+) S4 (D2-) 49 - 20 G4 (G2-) S3 (D1+) 50 = = 19 G3 (G1+) S2 (D1-) 51 - 18 G2 (G1-) S1 (D0+) 52 - 17 G1 (G0+) S0 (D0-) 53 = = 16 G0 (G0-) ANALOG GROUND 54 P 15 ANALOG GROUND RESERVED 55 = = 14 DIGITAL GROUND RESERVED 56 - 13 DIGITAL GROUND RESERVED 57 - 12 +5 VOLTS ANALOG EXPANSION BIT 4 58 P 9 11 DIGITAL GROUND ANALOG EXPANSION BIT 3 59 - 10 DIGITAL GROUND ANALOG EXPANSION BIT 2 60 P 9 +5 VOLTS ANALOG EXPANSION BIT 1 61 = 8 DIGITAL GROUND ANALOG EXPANSION BIT 0 62 - 7 DIGITAL GROUND INTERNAL OUTPUT CLOCK - OUTPUT (OUTCLK) 63 - 6 +5 VOLTS EXTERNAL OUTPUT TRIGGER (OXTIN) 64 = 5 DIGITAL GROUND EXTERNAL OUTPUT CLOCK - INPUT (OXCIN) 65 🛛 🗗 4 DIGITAL GROUND INTERNAL INPUT CLOCK - OUTPUT (INCLK) 66 - 3 +5 VOLTS EXTERNAL INPUT TRIGGER (IXTIN) 67 - 2 DIGITAL GROUND EXTERNAL INPUT CLOCK - INPUT (IXCIN) 68 😐 😐 1 DIGITAL GROUND

Note: Use the pin numbering on this chart, rather than numbers which may be found on your connector. Connectors from different manufacturers are not numbered consistently.

Single-ended inputs are indicated by S0 through S15; their corresponding ground inputs are G0 through G15. Differential inputs are indicated by D0- and D0+ through D7- and D7+; their corresponding ground inputs are G0- and G0+ through G7- and G7+. Every differential signal must be referenced to the corresponding ground. Data Acquisition Processors have a limited common mode voltage range and a ground connection must be used to assure that this range is not exceeded.

A single-ended analog signal should be connected to an analog input pin and to an analog ground pin, for example to pins 53 and 16. A differential analog signal should be connected to two adjacent analog input pins and either of their corresponding grounds, for example to input pins 52, 53, and ground pin 16 or 17.

Termination boards to connect all lines of the analog connector to discrete wires are available from Microstar Laboratories.

The DAP 1200a and DAP 2400a feature fault-protected input multiplexers. Fault protected input multiplexers allow signals to be connected to the Data Acquisition Processor with power off and allow a higher input voltage without damaging the inputs. Spare fault-protected input multiplexers are available from Microstar Laboratories.

Analog input signals should be within the range from -25 volts to +25 volts, relative to the ground of the Data Acquisition Processor. Input signals may be applied to the Data Acquisition Processor when the PC's power is off. See Chapter 5 for electrical characteristics of the analog input pins.

The analog I/O connector of the Data Acquisition Processor includes digital-to-analog converter output pins and analog power supply voltages. Pins 36 and 37 are the outputs of DAC0 and DAC1, respectively. Pins 33 and 32 are the grounds for DAC0 and DAC1, respectively. The digital-to-analog converters have voltage outputs with typical output impedance of 0.2 Ohms. These normally should drive high impedance inputs. The output current from each digital-to-analog converter output is rated at  $\pm 5$  milliamps, but it is recommended that this current not exceed  $\pm 1$  milliamp.

Analog outputs are set to zero when the system is first powered on. When analog outputs are configured for unipolar mode, the outputs are set to half of the full scale range when the system is first powered on. When J32 is moved, the analog outputs at power-on may vary by up to 5 millivolts.

Pin 15 is analog power ground. Pins 34 and 35 are connected to +18 volt and -18 volt analog power supplies. The maximum allowable current drain from these supplies is 20 milliamps per side. These supplies can be used for low current, low noise devices such as external multiplexers. To supply power to other devices, either use an external supply or use the 5-volt digital power supply found on the analog control connector with an external DC-to-DC converter.

The analog I/O connector also provides analog input expansion control lines, an external trigger input, an external input clock input, an internal input clock output, and connections to the 5-volt digital supply and its ground.

Pins 62-58 provide TTL-compatible analog input expansion control signals that select the expansion port. The five highest order bits of the input pin number appear in descending order on pins 58, 59, 60, 61, and 62 for a period starting one sample time before the analog input is sampled.

External analog input expansion boards are available from Microstar Laboratories. Each input expansion board allows up to 32 differential inputs, or up to 64 singleended inputs, or any combination requiring up to 64 input lines. A Data Acquisition Processor can control up to 8 external analog input expansion boards, for a total of 512 input lines.

The analog I/O connector has an input pin for an active high external trigger. Sampling is inhibited if the external trigger is inactive when an input procedure is started. Sampling then commences on the inactive to active transition.

The external trigger is either one-shot or gated, depending on the HTRI GGER command in the active input procedure. The external trigger is ignored if there is no HTRI GGER command in the active input procedure. See Chapter 6 for more information.

An external trigger signal must be within the standard TTL logic range of 0 to +5 volts. The Data Acquisition Processor provides a pull-up resistor on the external trigger input. This forces the trigger input active if it is left unconnected.

Clock and trigger inputs may have signals applied when the Data Acquisition Processor is off.

The analog I/O connector has input and output pins for an external input clock. The input pin should be used to connect an external input clock. The output pin is the buffered output of the internal clock circuit. See Chapter 6 for more information.

Pins 3, 6, 9, and 12 provide +5 volt power. Maximum current from the +5 volt supply is 1 Amp.

DAP 1200a & DAP 2400a Connectors

32

#### **Digital Input/Output Connector**

The digital input/output connector is a vertical 100-pin connector labeled J1 DIGITAL IN/OUT. This connector is near the right edge the Data Acquisition Processor, to the left of the analog input/output connector. The digital I/O connector has two rows of 50 pins on 0.050 inch centers. This connector is manufactured by AMP, part number 1-104549-0. The digital I/O connector mates with insulation displacement connector AMP 1-111196-6.

The digital I/O connector is not accessible from the back of the PC. A cable, part number MSCBL 042, that makes the digital connector accessible at the adjacent slot in the PC is available from Microstar Laboratories. For systems that comply with the European EMC Directive, MSCBL 046 provides the same functionality as MSCBL 042 but with a shielded connector. Contact Microstar Laboratories for more details.

The pin numbering of the digital input/output connector is shown in the following diagram:

| RESERVED<br>DIGITAL GROUND51• 50RESERVEDDOUT 15<br>DOUT 1552• 49+5VOLTSDOUT 14<br>DOUT 1453• 48DIGITAL GROUNDDOUT 14<br>DOUT 1355• 46DIGITAL GROUNDDOUT 12<br>DOUT 1256• 45+5VOLTSDOUT 11<br>DOUT 1257• 44DIGITAL GROUNDDOUT 1058• 43DIGITAL GROUND |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL GROUND52• 49+5 VOLTSDOUT 1553• 48DIGITAL GROUNDDOUT 1454• 47DIGITAL GROUNDDOUT 1355• 46DIGITAL GROUNDDOUT 1256• 45+5 VOLTSDOUT 1157• 44DIGITAL GROUNDDOUT 1058• 43DIGITAL GROUND                                                            |

| DOUT 1454•47DIGITAL GROUNDDOUT 1355•46DIGITAL GROUNDDOUT 1256•45+5 VOLTSDOUT 1157•44DIGITAL GROUNDDOUT 1058•43DIGITAL GROUND                                                                                                                        |

| DOUT 1355•46DIGITAL GROUNDDOUT 1256•45+5 VOLTSDOUT 1157•44DIGITAL GROUNDDOUT 1058•43DIGITAL GROUND                                                                                                                                                  |

| DOUT 1256•45+5 VOLTSDOUT 1157••44DIGITAL GROUNDDOUT 1058••43DIGITAL GROUND                                                                                                                                                                          |

| DOUT 1157•44DIGITAL GROUNDDOUT 1058••43DIGITAL GROUND                                                                                                                                                                                               |

| DOUT 10 58 • • 43 DIGITAL GROUND                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                     |

| DOUT 9 59 • 42 DIGITAL GROUND                                                                                                                                                                                                                       |

| DOUT 8 60 • • 41 +5 VOLTS                                                                                                                                                                                                                           |

| DOUT 7 61 • • 40 DIGITAL GROUND                                                                                                                                                                                                                     |

| DOUT 6 62 • • 39 DIGITAL GROUND                                                                                                                                                                                                                     |

| DOUT 5 63 • • 38 DIGITAL GROUND                                                                                                                                                                                                                     |

| DOUT 4 64 • 37 +5 VOLTS                                                                                                                                                                                                                             |

| DOUT 3 65 • • 36 DIGITAL GROUND                                                                                                                                                                                                                     |

| DOUT 2 66 • • 35 DIGITAL GROUND                                                                                                                                                                                                                     |

| DOUT 1 67 • • 34 DIGITAL GROUND                                                                                                                                                                                                                     |

| DOUT 0 68 • • 33 +5 VOLTS                                                                                                                                                                                                                           |

| INTERNAL OUTPUT CLK - OUTPUT   69 • • 32 DIGITAL GROUND                                                                                                                                                                                             |

| RESERVED 70 • • 31 DIGITAL GROUND                                                                                                                                                                                                                   |

| RESERVED 71 • • 30 DIGITAL GROUND                                                                                                                                                                                                                   |

| RESERVED 72 • • 29 +5 VOLTS                                                                                                                                                                                                                         |

| RESERVED 73 • • 28 DIGITAL GROUND                                                                                                                                                                                                                   |

| RESERVED 74 • 27 DIGITAL GROUND                                                                                                                                                                                                                     |

| RESERVED 75 • • 26 DIGITAL GROUND                                                                                                                                                                                                                   |

| RESERVED 76 • 25 +5 VOLTS                                                                                                                                                                                                                           |

| RESERVED 77 • • 24 DIGITAL GROUND                                                                                                                                                                                                                   |

| RESERVED 78 • • 23 DIGITAL GROUND                                                                                                                                                                                                                   |

| RESERVED 79 • • 22 DIGITAL GROUND                                                                                                                                                                                                                   |

| DX2 80 • • 21 +5 VOLTS                                                                                                                                                                                                                              |

| DX1 81 • • 20 DIGITAL GROUND                                                                                                                                                                                                                        |

| DX0 82 • • 19 DIGITAL GROUND                                                                                                                                                                                                                        |

| INTERNAL INPUT CLK - OUTPUT 83 • • 18 DIGITAL GROUND                                                                                                                                                                                                |

| DIN 15 84 • 17 +5 VOLTS                                                                                                                                                                                                                             |

| DIN 14 85 • 16 DIGITAL GROUND                                                                                                                                                                                                                       |

| DIN 13 86 • • 15 DIGITAL GROUND                                                                                                                                                                                                                     |

| DIN 12 87 • • 14 DIGITAL GROUND                                                                                                                                                                                                                     |

| DIN 11 88 • • 13 +5 VOLTS                                                                                                                                                                                                                           |

| DIN 10 89 • 12 DIGITAL GROUND                                                                                                                                                                                                                       |

| DIN 9 90 • • 11 DIGITAL GROUND                                                                                                                                                                                                                      |

| DIN 8 91 • • 10 DIGITAL GROUND                                                                                                                                                                                                                      |

| DIN 7 92 • • 9 +5 VOLTS                                                                                                                                                                                                                             |

| DIN 6 93 • • 8 DIGITAL GROUND                                                                                                                                                                                                                       |

| DIN 5 94 • • 7 DIGITAL GROUND                                                                                                                                                                                                                       |

| DIN 4 95 • • 6 DIGITAL GROUND                                                                                                                                                                                                                       |

| DIN 3 96 • • 5 +5 VOLTS                                                                                                                                                                                                                             |

| DIN 2 97 • • 4 DIGITAL GROUND                                                                                                                                                                                                                       |

| DIN 1 98 • • 3 DIGITAL GROUND                                                                                                                                                                                                                       |

| DIN 0 99 • • 2 DIGITAL GROUND                                                                                                                                                                                                                       |

| +5 VOLTS 100 • • 1 DIGITAL GROUND                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                     |

Pins 1 and 100 are closest to the gold edge fingers of the Data Acquisition Processor.

Digital inputs are indicated by DINO-15 and digital outputs are indicated by DOUTO-15. Bit 0 is the least significant bit.

A termination board from Microstar Laboratories, part number MSTB 008, connects all lines of the digital connector to discrete wire connectors.

The digital inputs are FCT TTL with 10K pull-up resistors. The digital inputs sink no more than 5 microamps for a "1" input and source no more than 0.5 milliamps for a "0" input. An input voltage greater than 2 V is interpreted as a "1" and an input voltage less than 0.8 V is interpreted as a "0". When no signal is connected a digital input is read as a "1" due to the pull-up resistors.

Digital inputs may have TTL signals applied when the Data Acquisition Processor is off.

Digital output polarity at power-on is selected by J32, the Digital Output Reset Polarity Jumper, described later in this chapter.

The digital outputs are FCT TTL; they can sink no more than 12 milliamps for a "0" output and can source no more than 15 milliamps for a "1" output. The output voltage for a "1" is greater than 2.4 V and the output voltage for a "0" is less than 0.50 V.

The digital input/output connector has multiple connections for the Data Acquisition Processor +5 V power supply. The supply current is rated at 500 milliamps per connection with a total current limit of 2 Amps. The 2 Amp current limit is due to the limited current available from the host computer.

Pins 80, 81, and 82 provide TTL-compatible digital input expansion control signals. The low-order bit of the port number appears on pin 82, the middle bit appears on pin 81, and the high-order bit appears on pin 80.

An optional digital input port may be specified in a DAPL SET command. The digital input port numbers range from 0 to 7. The specified port number appears on the control pins for a period starting one sample time before the time at which the digital inputs are sampled. The port number can be used to control external multiplexers.

An external digital expansion board is available from Microstar Laboratories. Each external expansion board allows up to 64 digital inputs and 64 digital outputs. Each Data Acquisition Processor may be expanded to have a maximum of 128 digital inputs and 1024 digital outputs.

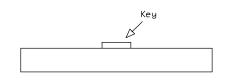

The Microstar Laboratories cable MSCBL 036-01 is compatible with the digital input/output port. The diagram below shows the key on the cable MSCBL036-01. This key must be towards the left side of the Data Acquisition Processor.

Note: Cables not made by Microstar Laboratories may have different keys.

#### **Output Clock Connector**

Connector J15 is a five-pin connector, Molex part number 22-23-2051; the mating connector is Molex part number 22-01-3057. J15 is located on the lower edge of the Data Acquisition Processor, between the 80186 CPU and the gold edge fingers.

The output clock signals and the output trigger signal are available on connector J15, along with power and ground. These signal pins can be used to control when outputs are updated. See Chapter 6 for more details.

The pin numbering for J15 is given in the following table:

#### Shunts

Several of the Data Acquisition Processor options are set by shunts. These are jumper wires enclosed in plastic, designed for connecting pins on 0.100" centers.

Each shunt has a top and a bottom. When a shunt is placed correctly, a probe point is visible in the shunt. Shunts must not be placed upside down on the pins, as incorrectly placed shunts do not provide reliable contacts.

#### **Analog Signal Path Selection**

In addition to the DAPL configuration options, the Data Acquisition Processor has several hardware configuration options. These determine the path taken by analog signals from the input pins to the analog-to-digital converter.

The analog signal path between the input pins and the analog-to-digital converter consists of the following functional units:

- 1. input multiplexers

- 2. instrumentation amplifier

- 3. programmable gain amplifier

- 4. range amplifier

- 5. analog-to-digital converter with sample-and-hold amplifier

Analog signals must pass through the input multiplexers, the instrumentation amplifier, and the analog-to-digital converter. Jumpers determine whether the analog signal path includes the programmable gain amplifier and the unipolar offset circuit, and also determine the input voltage range.

A signal range is called bipolar if it includes both positive and negative voltages; a signal range is called unipolar if it includes voltages of only one sign. The range amplifier allows the bipolar analog-to-digital converter to operate with unipolar voltages. Jumpers select from three bipolar ranges and one unipolar range. If the programmable gain amplifier is enabled, gains of 1, 10, 100, and 500 are software selectable.

#### **Analog Signal Path Configuration**

Two connectors control the analog signal path of the DAP 1200a and DAP 2400a. Note that changing voltage ranges may require recalibration.

The following table summarizes the DAP 1200a and DAP 2400a jumper connections:

| ADC Range | J7  | J8        |  |  |  |  |

|-----------|-----|-----------|--|--|--|--|

| 0v to 5v  | 2   | 1-8,3-6   |  |  |  |  |

| ±5v*      | 1 * | 3-6,4-5 * |  |  |  |  |

| ±10v      | 1   | 3-4,5-6   |  |  |  |  |

| * F · C C |     |           |  |  |  |  |

\* Factory Configuration

The input signal to the unipolar offset circuit is selected by J7:

| J 7 |   |   |  |

|-----|---|---|--|

| 1   | 2 | 3 |  |

| •   |   | • |  |

| 1   | 2 | З |  |

Exactly one jumper should be placed on J7, as follows:

| Jumper | Signal range           |  |  |  |

|--------|------------------------|--|--|--|

| 1      | unipolar               |  |  |  |

| 2      | bipolar, gain enabled  |  |  |  |

| 3      | bipolar, gain disabled |  |  |  |

The unipolar input range is from 0 to +5 volts.

The input signal to the analog-to-digital converter is selected by J8, which selects the input voltage range as well as enabling or disabling gain if in bipolar mode. It is often desirable to leave gain enabled, even if only a gain of 1 is used.

| 5 |   | • 4 |

|---|---|-----|

| 5 | • | •4  |

| 6 | 0 | • 3 |

| 7 | • | • 2 |

| 8 | 0 | • 1 |

|   |   |     |

|   |   | J8  |

Exactly two jumpers should be placed on J8, as follows:

| Jumpers  | Signal range                      |

|----------|-----------------------------------|

| 1-8, 3-6 | unipolar, 0 to 5 Volts            |

| 4-5, 3-6 | bipolar, ±5 Volts, gain enabled   |

| 2-7, 3-6 | bipolar, ±5 Volts, gain disabled  |

| 3-4, 5-6 | bipolar, ±10 Volts, gain enabled  |

| 3-4, 6-7 | bipolar, ±10 Volts, gain disabled |

Note that jumpers on J8 may be placed horizontally or vertically.

Note: Regardless of the input voltage range, positive and negative differential signals may range from -10 volts to +10 volts.

#### **Channel List Selection**

The Data Acquisition Processor has two possible external input clocking modes. When Channel List Clocking is enabled, all input pins are sampled on each low to high transition of the external clock. When Channel List Clocking is disabled, a single pin is sampled on each low to high transition of the external clock.

Connector J16, located above the left-most gold edge connector, determines the clocking mode for external clocking. J16 is a three pin vertical header of one column on 0.100 inch centers. The factory configuration is "enabled."

| J16 | ۵3 |

|-----|----|

|     | •2 |

|     | ●1 |

|     |    |

Exactly one jumper should be placed on J16, as follows:

| Pins | Channel List Clocking |

|------|-----------------------|

|      |                       |

| 2,3 | disabled |

|-----|----------|

| 1,2 | enabled  |

#### **Analog Output Voltage Range Selection**

The voltage ranges of DAC0 and DAC1 are selected by headers J11 and J12, respectively:

| J | 12     |        |        |        |   |        |        |        |   |  |        |        |        |        |        |   |        | J      | 11 |

|---|--------|--------|--------|--------|---|--------|--------|--------|---|--|--------|--------|--------|--------|--------|---|--------|--------|----|

|   | 1<br>• | 2<br>• | 3<br>● | 4<br>• | 5 | 6<br>• | 7<br>• | 8<br>• |   |  | 1<br>• | 2<br>9 | 9<br>9 | 4<br>• | 5<br>• | 6 | 7<br>• | 8<br>• |    |

|   |        |        | DA     | \C 1   |   |        |        |        | • |  |        |        | D      | AC     | 0      |   |        |        |    |

Three jumpers should be placed on J11 and J12, as follows:

| Jumpers                | Range                  |

|------------------------|------------------------|

| 3 to 4, 5 to 6, 7 to 8 | 0 volts to +10 volts   |

| 1 to 2, 4 to 5, 7 to 8 | -5 volts to +5 volts   |

| 1 to 2, 4 to 5, 6 to 7 | -10 volts to +10 volts |

Note: By default, DAPL assumes that the outputs of the digital-to-analog converters are bipolar. If a unipolar output range is selected, the following DAPL command must be issued:

OPTION BPOUTPUT=OFF

#### **Digital Output Reset Polarity Jumper**

The digital output reset polarity jumper J32 has two pins spaced at 0.100". J32 is located near the center of the Data Acquisition Processor, approximately 2.5" above J15. The digital output reset polarity jumper allows selection of the digital output polarity at power-on. If J32 is installed, all digital outputs will be reset to 0 at power-on. If J32 is removed, all digital outputs will be preset to 1 at power-on. All Data Acquisition Processors are shipped from the factory with J32 installed. The voltage of the analog outputs at reset may vary by up to 5 millivolts when J32 is removed.

#### Input/Output Synchronization Header

The input/output synchronization header J22 has two pins spaced at 0.100". J22 is located approximately one inch above the left set of gold fingers on the Data Acquisition Processor. If a shunt is placed on J22, the input trigger is connected to the output update clock. This causes a hardware input trigger to occur when an output procedure initiates its first update. This is used to synchronize input sampling to output updates.

#### **Synchronization Connector**

The synchronization connector J13 has a single row of five pins on 0.100 inch centers. J13 is located at the upper left of the Data Acquisition Processor printed circuit board. The synchronization connector allows several Data Acquisition Processors to share the same sampling clock. See the Systems Manual for more information about using synchronous Data Acquisition Processors.

For synchronization, the shared sampling clock requires special cabling between Data Acquisition Processors. The analog sampling clock of the master unit is supplied to the slave units by means of the cable MSCBL 015-01. Contact Microstar Laboratories for more information about cabling for synchronous Data Acquisition Processors.

## 5. Analog Input Circuits

The analog input hardware of the Data Acquisition Processor is discussed in some detail in this chapter. The following summary gives sufficient information for most Data Acquisition Processor applications:

- The DC input impedance is very high.

- At high sampling rates, the signal source impedance should be low.

- Minimum sampling times are specified for unity gain.

- At gain 10, the fastest sampling rate is slower than the fastest sampling rate at gain 1.

- At gain 100 and 500, the fastest sampling rate is substantially slower than the fastest sampling rate at gain 1.

#### **Analog Input Circuits**

Data Acquisition Processor analog input signals pass through two analog multiplexers and then to an op amp with a FET input. The DC input impedance is very high, typically far in excess of 10M Ohms. The AC input impedance is dominated by the capacitance of the multiplexers.

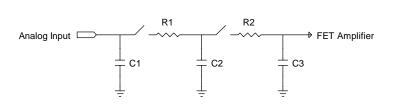

Figure 3 shows a useful equivalent circuit for each Data Acquisition Processor input. As the Data Acquisition Processor scans through the input pins defined by an input procedure, the switches in the multiplexers open and close, connecting the specified inputs to multiplexer outputs. When an input signal is connected to the FET amplifier, the signal source must supply sufficient current to charge the equivalent capacitance of the multiplexers before the analog-to-digital conversion can start.

Figure 3

**Analog Input Circuits**

The DAP 1200a and DAP 2400a have fault-protected multiplexers. The following table shows typical resistance and capacitance values, in Ohms and picofarads, for fault-protected multiplexers.

| Value |

|-------|

| 300Ω  |

| 100Ω  |

| 5 pF  |

| 55 pF |

| 30 pF |

|       |

## **Programmable Gain Amplifier**

At gains other than unity, the programmable gain amplifier requires extra time to switch from pin to pin and then settle to full accuracy. The following table shows typical minimum sampling times for each Data Acquisition Processor at each gain.

| Model   | Minim | um Sample T | Times in μS at | Gain: |

|---------|-------|-------------|----------------|-------|

|         | 1     | 10          | 100            | 500   |

| 1200a/4 | 6.00  | 8           | 40             | 500   |

| 1200a/6 | 3.20  | 8           | 40             | 500   |

| 2400a/4 | 6.00  | 8           | 40             | 500   |

| 2400a/5 | 4.00  | 8           | 40             | 500   |

| 2400a/6 | 3.20  | 8           | 40             | 500   |

**Analog Input Circuits**

## 6. Clocks and Triggers

The Data Acquisition Processor is designed to operate using either internal clocks or external clocks. The Data Acquisition Processor has onboard crystal-controlled timers to provide an internal input sampling rate and output update rate, and also has provisions for external clocks for both input and output.

The Data Acquisition Processor has hardware control lines for an input clock, an output clock and an input trigger. These lines all are TTL compatible. The input clock and the output clock both are positive-edge triggered.

The input clock on all models has two modes. In the first mode, called Channel List Clocking, the Data Acquisition Processor starts conversion of an entire channel list on the positive edge of the clock. In the second mode, the Data Acquisition Processor converts a single channel on the positive edge of the clock.

The input trigger and output trigger on all models also have two modes, a one-shot mode and a level triggered gate mode.

## Software Triggers vs. Hardware Triggers for Input

DAPL provides a powerful software triggering mechanism which is suitable for most applications. For those applications which require precise synchronization to external hardware or which are too fast to take advantage of software triggering, hardware triggering is provided. Software triggering is more versatile than hardware triggering. In applications with sampling rates of less than 10 KHz, software triggering almost always provides a better solution than hardware triggering.